Die Elektronikbranche steht vor einem Paradoxon: Geräte werden immer kompakter, während ihre Funktionalität exponentiell wächst. Smartphones vereinen heute mehr Rechenleistung als Raumfahrtcomputer vergangener Jahrzehnte – auf einer Fläche, die in die Hosentasche passt. Diese Miniaturisierung wäre ohne High Density Interconnect-Technologie undenkbar.

Der Umstieg auf HDI-Leiterplatten erscheint auf den ersten Blick als reine Platzoptimierung. Doch dieser Eindruck greift zu kurz. Die wahre ökonomische Bedeutung entfaltet sich erst in der Gesamtkostenbetrachtung: Von direkten Materialeinsparungen über reduzierte Fertigungskosten bis hin zu Kaskadeneffekten in Logistik und Produktlebenszyklus.

Die folgende Analyse verfolgt einen systematischen Ansatz: von unmittelbaren Einsparpotenzialen durch Lagenreduktion über indirekte Systemeffekte bis zur kritischen Bewertung von Rentabilitätsschwellen. Denn HDI ist keine Universallösung – erst die Kenntnis der Mechanismen und Grenzen ermöglicht wirtschaftlich fundierte Entscheidungen.

HDI-Kostenanalyse im Überblick

HDI-Technologie senkt Kosten durch mehrschichtige Effekte: Mikrovia-Architektur reduziert Lagenzahl um 40-60%, was Material und Gewicht spart. Diese Kompaktheit löst Kaskadeneffekte aus – kleinere Gehäuse, optimierte Logistik, reduzierte Transportkosten. Die Rentabilität hängt vom Produktionsvolumen ab: Bei Consumer Electronics amortisiert sich HDI ab 5.000 Einheiten, bei Medizintechnik bereits ab 1.000 Stück. Entscheidend ist die TCO-Betrachtung statt isolierter Stückpreise, da Entwicklungs-, Fertigungs- und Garantiekosten über den Lebenszyklus 75-85% der Gesamtkosten ausmachen. Designfehler wie Überspezifikation oder ungenutzte Mikrovia-Potenziale können theoretische Einsparungen jedoch zunichtemachen.

Von der Materialeinsparung zur Gesamtkostenrechnung: Der wahre Wert von HDI

Die meisten Entscheider betrachten Leiterplatten durch eine verzerrte ökonomische Linse: Der Einkaufspreis pro Einheit dominiert die Bewertung. Diese Perspektive ignoriert jedoch systematisch 75-85% der tatsächlichen Kosten, die über den gesamten Produktlebenszyklus anfallen.

Der Stückpreis einer HDI-Leiterplatte liegt typischerweise 20-40% über konventionellen Multilayer-Designs. Diese Mehrkosten schrecken ab – bis die Gesamtkostenrechnung offenbart, dass der PCB-Preis nur einen Bruchteil der Systemkosten repräsentiert. Entwicklungsaufwand, Prototyping, Bestückung, Qualitätssicherung, Ausfallraten und Garantieabwicklungen summieren sich zur dominanten Kostenmasse.

Die Analyse der Total Cost of Ownership (TCO) macht sichtbar, wovon während der gesamten Lebensdauer und Einsatzdauer des Produkts die Kosten massgeblich abhängen

– Business-Wissen.de Redaktion, Business-Wissen TCO-Ratgeber

Eine vollständige TCO-Methodik integriert sichtbare und verborgene Kostenkomponenten. Zu den sichtbaren Kosten zählen Material, Lagenzahl und Fertigungsaufwand. Die verborgenen Kostentreiber umfassen längere Entwicklungszyklen bei konventionellen Designs, höhere Ausschussraten durch komplexere Bestückung, grössere Gehäuse mit Materialaufwand sowie Logistikkosten für Transport und Lagerung voluminöser Baugruppen.

HDI-Technologie verschiebt diese Kostenstruktur fundamental. Durch Lagenreduktion sinken nicht nur Materialkosten, sondern auch Fertigungszeiten und Fehlerquoten. Die kompaktere Bauweise reduziert Transportvolumen und ermöglicht dichtere Lagerung. Diese Effekte multiplizieren sich über hohe Stückzahlen und lange Produktlebenszyklen.

| Technologie | Typische Lagenzahl | Platzbedarf | Gewicht |

|---|---|---|---|

| Standard-Multilayer | 16-20 Lagen | 100% | 100% |

| HDI-Technologie | 8-10 Lagen | 60-70% | 50-60% |

| HDI Anylayer | 6-8 Lagen | 40-50% | 35-45% |

Die Tabelle verdeutlicht die primären Einsparungen, doch die eigentliche Wirtschaftlichkeit entsteht durch sekundäre und tertiäre Effekte. Ein 8-Lagen-HDI-Design ersetzt nicht nur einen 16-Lagen-Standardaufbau – es verändert die gesamte Wertschöpfungskette vom Engineering bis zum After-Sales-Service.

Entscheidend für die Bewertung sind drei Metriken: Kosten pro Funktion (was kostet die Implementierung einer spezifischen elektrischen Eigenschaft), Kosten pro Volumeneinheit des Endprodukts (€/cm³) und Lebenszykluskosten über die Garantiedauer. Diese Kennzahlen ermöglichen Vergleiche jenseits oberflächlicher Stückpreise.

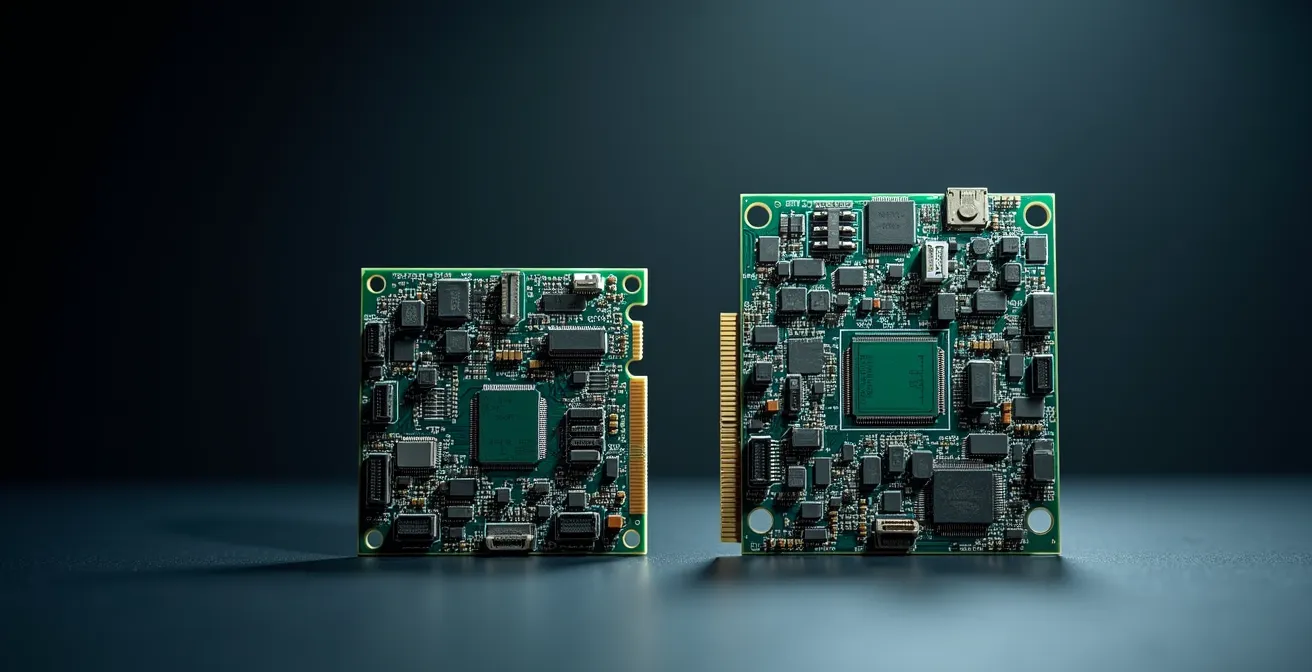

Der visuelle Vergleich zwischen konventionellem Multilayer-Aufbau und HDI-Architektur offenbart die strukturelle Differenz. Während durchgehende Vias bei Standarddesigns alle Lagen durchdringen und damit Routing-Fläche blockieren, verbinden Mikrovias bei HDI gezielt einzelne Lagenpaare. Diese Selektivität setzt Designpotenzial frei und ist der Schlüssel zur Lagenreduktion.

Wie Mikrovia-Architektur Lagenzahl und Platzbedarf systematisch reduziert

Die Mikrovia-Technologie revolutioniert die Leiterplattenarchitektur durch einen fundamentalen Paradigmenwechsel: Statt mechanisch gebohrter Durchkontaktierungen mit 0,3-0,4 mm Durchmesser ermöglichen laserstrukturierte Mikrovias Verbindungen von nur 0,1-0,15 mm. Diese Dimensionsreduktion erscheint marginal, entfaltet jedoch kaskadierende Auswirkungen auf die gesamte Designphilosophie.

Konventionelle Vias durchdringen alle Leiterplattenlagen – ein 8-Lagen-Board erfordert Bohrungen von der Oberfläche bis zur Unterseite. Jedes Via blockiert damit Routing-Kanäle auf allen Zwischenlagen, selbst wenn die elektrische Verbindung nur zwei Lagen betreffen sollte. Bei hohen Komponentendichten mit 0,4-0,5 mm Pitch BGA-Gehäusen wird diese Ineffizienz zum limitierenden Faktor.

Mikrovias durchbrechen diese Beschränkung durch drei Architekturen: Blind Vias verbinden Aussenlagen mit inneren Lagen ohne Durchdringung der gesamten Platine. Buried Vias verknüpfen innere Lagen untereinander, bleiben aber von aussen unsichtbar. Stacked Vias erlauben die vertikale Stapelung mehrerer Mikrovias, wodurch Verbindungen über viele Lagen bei minimalem Flächenverbrauch möglich werden.

| Parameter | Standard-Via | Mikrovia | Platzersparnis |

|---|---|---|---|

| Bohrungsdurchmesser | 0.3-0.4mm | 0.1-0.15mm | 60-70% |

| Pad-Durchmesser | 0.6mm | 0.3mm | 50% |

| Annular Ring | 0.15mm | 0.1mm | 33% |

| Aspect Ratio | 8:1 | 1:1 | Bessere Zuverlässigkeit |

Die technischen Parameter offenbaren quantifizierbare Vorteile. Ein Mikrovia mit 0,1 mm Durchmesser benötigt einen Pad-Durchmesser von nur 0,3 mm – gegenüber 0,6 mm bei konventionellen Vias eine Flächenreduktion von 75%. Bei einem typischen BGA mit 400 Anschlüssen summiert sich diese Einsparung zu mehreren Quadratzentimetern freier Routing-Fläche.

Das günstigere Aspektverhältnis von 1:1 bei Mikrovias (Tiefe gleich Durchmesser) verbessert zudem die Zuverlässigkeit der Durchkontaktierung. Konventionelle Vias mit Aspektverhältnissen von 8:1 oder höher sind anfällig für unvollständige Kupfermetallisierung in engen Bohrungen – ein Hauptgrund für Fertigungsausfälle und Feldausfälle.

Ein konkretes Designbeispiel verdeutlicht die Einsparung: Ein 10-Lagen-Standarddesign mit konventionellen Vias für ein Smartphone-Mainboard erfordert typischerweise 140 x 70 mm Fläche. Durch Mikrovia-Architektur lässt sich dieselbe Funktionalität auf einem 6-Lagen-HDI-Design mit 120 x 65 mm realisieren – eine Flächenreduktion von 34% und eine Dickenreduktion von 1,6 mm auf 0,8 mm.

Diese Kompaktierung ermöglicht das Routing zwischen den Pads von Fine-Pitch-BGAs, was bei konventioneller Technologie unmöglich ist. Bei 0,4 mm Pitch verbleiben zwischen den Pads nur 0,15 mm – zu wenig für Standard-Vias mit 0,3 mm Durchmesser plus Clearance. Mikrovias mit 0,1 mm passen problemlos in diese Lücken und eliminieren die Notwendigkeit zusätzlicher Lagen für Escape-Routing.

HDI-Design-Checkliste für optimale Lagenreduktion

- Mikrovia-Durchmesser durch Aussenlagendicke vorgegeben prüfen

- Impedanz- und Aufbauvorgaben mit Fertiger vorab diskutieren

- Kontaktierungs- und Aufbauvarianten evaluieren

- Aspect Ratio bei gegebener Lagendicke berücksichtigen

- HDI-Technologie ab 500 MHz fast immer erforderlich

Die Checkliste adressiert kritische Designentscheidungen. Besonders die Abstimmung mit dem Fertiger vor Layoutbeginn verhindert kostspielige Redesigns. Impedanzvorgaben determinieren Lagenaufbau und Materialwahl – Parameter, die nachträglich nur mit erheblichem Aufwand korrigierbar sind.

Kaskadeneffekte kompakter Bauweise: Gehäuse, Logistik und Systemkosten

Die Lagenreduktion und Miniaturisierung durch HDI-Technologie endet nicht an den Platinenkanten. Jeder eingesparte Millimeter Platinenfläche und Dicke setzt eine Kettenreaktion ökonomischer Effekte frei, die sich durch die gesamte Wertschöpfungskette ziehen – vom Produktdesign über Fertigung und Logistik bis zur Nutzungsphase.

Ein kompakteres PCB ermöglicht proportional kleinere Gehäuse. Bei Consumer Electronics, wo Produktgrösse kaufentscheidend ist, eröffnet dies Wettbewerbsvorteile. Doch selbst bei Industrieanwendungen, wo Grösse sekundär erscheint, generieren kleinere Gehäuse messbare Einsparungen: 30% Volumenreduktion bedeutet 20-40% weniger Kunststoff oder Metallverbrauch bei der Gehäusefertigung.

Das reduzierte Gewicht multipliziert Einsparungen im Transportsektor. Luftfracht für Elektronikprodukte wird volumetrisch oder nach Gewicht abgerechnet – je nachdem, welcher Wert höher liegt. Eine Gewichtsreduktion von 40% durch HDI-Einsatz senkt Frachtkosten direkt. Bei Jahresvolumina von 100.000 Einheiten und transkontinentalen Lieferketten summieren sich diese Einsparungen auf fünf- bis sechsstellige Beträge.

Logistikoptimierung manifestiert sich auch in der Lagerhaltung. Kompaktere Produkte erhöhen die Einheitendichte pro Palettenplatz um 30-50%. Distributionszentren können mit identischer Fläche höhere Volumina bevorraten, was Lagerkosten pro Einheit senkt. Für Produkte mit langen Durchlaufzeiten oder saisonalen Spitzen reduziert dies Working Capital-Bindung merklich.

Die Progression von voluminösen zu ultrakompakten Elektronikprodukten ist nur durch konsequente HDI-Implementierung möglich. Smartphones, Wearables und medizinische Implantate wären in heutiger Form ohne Mikrovia-Technologie technisch nicht realisierbar. Diese Produktkategorien repräsentieren Märkte mit dreistelligen Milliardenumsätzen – geschaffen durch Miniaturisierungstechnologie.

Thermische Systemeffekte bieten weitere Einsparungspotenziale. Kleinere Gehäusevolumina benötigen weniger Kühlleistung, da weniger Luftmasse zu zirkulieren ist. Bei passiv gekühlten Designs verbessert die kompaktere Bauweise die Wärmeabfuhr, da kritische Komponenten näher an Gehäuseaussenflächen positioniert werden können. Dies eliminiert in manchen Fällen aktive Kühlung – eine Einsparung bei Kosten, Energieverbrauch und Ausfallrisiko.

Der ökologische Fussabdruck schrumpft parallel zur Produktgrösse. Reduzierter Materialeinsatz, geringerer Energieaufwand bei Transport und Kühlung sowie optimierte Raumausnutzung in Logistik senken CO₂-Emissionen über den Produktlebenszyklus. In Branchen mit strengen Nachhaltigkeitsvorgaben oder CSR-Zielen wird dies zum quantifizierbaren Wirtschaftsfaktor.

Die Digitalisierung durch moderne Elektronik beschleunigt sich durch solche Miniaturisierungssprünge. IoT-Sensoren, Edge-Computing-Module und embedded Systems werden erst durch kompakte, kosteneffiziente HDI-Designs in der Breite implementierbar.

Assemblierungskosten sinken ebenfalls. Kleinere Platinen durchlaufen Bestückungslinien schneller, benötigen weniger Handlingoperationen und reduzieren das Risiko mechanischer Beschädigungen. Bei automatisierter Fertigung mit Taktzeiten im Sekundenbereich summieren sich selbst marginale Zeitersparnisse zu signifikanten Kostendifferenzen bei Grossserien.

Rentabilitätsschwellen: Wann sich HDI-Investitionen tatsächlich amortisieren

Die bisherige Analyse demonstriert substanzielle Einsparpotenziale durch HDI-Technologie. Doch diese Vorteile materialisieren sich nicht automatisch – sie erfordern Vorlaufkosten und hängen kritisch von Produktionsvolumina, Anwendungscharakteristiken und Lebenszyklusdauer ab. Die Rentabilitätsfrage lässt sich nur kontextspezifisch beantworten.

HDI-Designs verursachen höhere Non-Recurring Engineering-Kosten (NRE). Komplexere Layoutregeln, aufwändigere Simulationen für Signalintegrität und mehrfache Abstimmungsschleifen mit Fertigern verlängern Entwicklungszyklen um 20-40%. Diese Fixkosten müssen über die Produktionsmenge amortisiert werden – der klassische Break-even-Point.

Für Consumer Electronics mit hohen Stückzahlen liegt dieser Schwellenwert typischerweise bei 5.000-10.000 Einheiten. Bei einem Smartphone-Mainboard mit 50.000 € NRE und 8 € Stückkosteneinsparung amortisiert sich die Investition bereits nach 6.250 Einheiten. Bei Produktionsvolumina von 500.000 Stück pro Jahr wird HDI zur wirtschaftlichen Selbstverständlichkeit.

Yields are very sensitive to min. diameter, annular rings, min. trace and spacing

– Happy Holden, HDI PCB Design Guidelines – Altium

Die Ausbeute bei HDI-Fertigung reagiert sensitiv auf Designparameter – ein kritischer Faktor für die Rentabilitätsberechnung. Zu aggressive Spezifikationen (Mikrovia-Durchmesser unter 0,1 mm, Leiterbahnbreiten unter 0,075 mm) können Ausschussraten von unter 5% auf über 20% steigern. Diese Ausfallkosten müssen in die TCO-Kalkulation einfliessen.

Für Medizintechnik verschieben sich die Schwellenwerte dramatisch. Hier dominieren Zuverlässigkeitsanforderungen und Zulassungskosten die Wirtschaftlichkeitsrechnung. Ein implantierbares Gerät mit 15 Jahren Lebensdauer rechtfertigt höhere Platinen-Stückkosten, wenn dadurch Ausfallraten sinken. Break-even tritt bereits bei 1.000-2.000 Einheiten ein, da Garantie- und Haftungskosten die primären Kostentreiber darstellen.

| Anwendungsbereich | Break-Even-Punkt | ROI-Zeitraum | Kritische Faktoren |

|---|---|---|---|

| Smartphone/Wearables | 5.000 Stück | 6-12 Monate | Miniaturisierung kritisch |

| Automotive ECU | 10.000 Stück | 18-24 Monate | Zuverlässigkeit, Temperatur |

| Medical Implants | 1.000 Stück | 12-18 Monate | Biokompatibilität, Grösse |

Die Tabelle verdeutlicht branchenspezifische Unterschiede. Automotive-Anwendungen zeigen längere ROI-Zeiträume trotz moderater Break-even-Punkte – bedingt durch ausgedehnte Qualifikationszyklen und konservative Einführungsstrategien. Die Automobilindustrie verlangt typischerweise 2-3 Jahre Felderprobung vor Serieneinsatz, was Cashflow-Betrachtungen kompliziert.

IoT-Anwendungen präsentieren ein differenziertes Bild. Bei batteriebetriebenen Edge-Nodes mit extremen Grössenbeschränkungen ist HDI alternativlos – hier existiert keine Rentabilitätsschwelle im klassischen Sinn, da konventionelle Technologie die Anforderungen nicht erfüllt. Anders bei industriellen IoT-Gateways ohne Platzbeschränkung: Hier überwiegen Standard-PCBs oft wirtschaftlich.

Der Produktlebenszyklus moduliert die Amortisationsrechnung fundamental. Consumer-Produkte mit 12-18 Monaten Marktlebensdauer müssen NRE-Kosten schnell zurückverdienen. Industrieausrüstung mit 10-15 Jahren Verfügbarkeitspflicht amortisiert HDI-Investitionen über längere Zeiträume, profitiert aber von kumulierten Einsparungen bei Wartung, Ersatzteilhaltung und Ausfallkosten.

Ein oft übersehener Faktor: Markteinführungsgeschwindigkeit. HDI ermöglicht kompaktere Designs ohne mechanische Redesigns des Gesamtprodukts. Bei Time-to-Market-kritischen Projekten rechtfertigt sich HDI durch beschleunigte Markteinführung – ein Vorteil, der sich nur indirekt monetarisieren lässt, aber Umsatzpotenziale von Monaten exklusiver Marktpräsenz erschliesst.

Die Fähigkeit, Technologie-Trends rechtzeitig erkennen zu können, wird zum Wettbewerbsvorteil. Unternehmen, die HDI-Kompetenz frühzeitig aufbauen, positionieren sich für Produktgenerationen, in denen Miniaturisierung vom Differentiator zur Hygienefaktor mutiert.

Designfallen, die HDI-Kostenvorteile zunichte machen

Die theoretischen Einsparpotenziale von HDI-Technologie materialisieren sich nur bei korrekter Implementierung. Zahlreiche Designentscheidungen können die ökonomischen Vorteile neutralisieren oder ins Gegenteil verkehren. Eine kritische Analyse häufiger Fehlerquellen ist unerlässlich für die Realisierung erwarteter ROI-Werte.

Überspezifikation rangiert als häufigster Kostentreiber. Designer spezifizieren oft HDI-Klasse 3 mit 8+ Lagen und Mikrovia-Durchmessern von 0,1 mm, obwohl Klasse 2 mit 6 Lagen und 0,15 mm Vias funktional ausreicht. Jede zusätzliche Lage erhöht Kosten um 15-25%, jede Reduktion des Mikrovia-Durchmessers um 0,05 mm steigert Ausschussraten um 3-8%. Diese Mehrkosten akkumulieren ohne funktionalen Gegenwert.

Unnötig enge Toleranzen verschärfen das Problem. Leiterbahnbreiten von 0,05 mm statt 0,075 mm oder Abstände von 0,075 mm statt 0,1 mm verdoppeln oft Fertigungskosten, ohne elektrische Performance zu verbessern. Die Spezifikation sollte sich an tatsächlichen Anforderungen orientieren – nicht an technologischen Möglichkeiten.

Konservative Designarchitekturen verschwenden HDI-Potenzial. Layouts, die Mikrovia-Routing zwischen BGA-Pads nicht nutzen, verzichten auf den Kernvorteil der Technologie. Komponenten, die nicht entsprechend der Mikrovia-Möglichkeiten gruppiert werden, erfordern zusätzliche Lagen für Signalführung. Unterbelegte Lagen verschwenden Material ohne Nutzen – ein 6-Lagen-HDI-Design mit nur 60% genutzter Routing-Fläche pro Lage hätte oft als 4-Lagen-Design realisiert werden können.

Materialwahl ohne funktionale Rechtfertigung treibt Kosten. FR-4 mit Tg 170°C genügt für die meisten Consumer-Anwendungen – die Spezifikation von Polyimid oder High-Tg-Materialien (Tg >180°C) erhöht Kosten um 40-80% ohne Performance-Gewinn bei Standardtemperaturbereichen. Nur bei Automotive-Anwendungen mit 125°C Dauertemperatur oder Lead-free-Reflow mit mehrfachen Durchläufen rechtfertigen sich Premium-Substrate.

Fertigungsfehler wie unvollständige Kupfermetallisierung, Voids in der Via-Füllung oder Delaminationen zwischen Lagen entstehen oft durch designseitige Ursachen. Zu hohe Aspektverhältnisse, inkompatible Materialstapel oder unzureichende thermische Symmetrie erzwingen Nacharbeit oder führen zu Ausschuss. Diese Fehlerkosten übersteigen schnell die initialen Materialeinsparungen.

Lieferantenkonsolidierung wird unterschätzt. Die Aufteilung von PCB-Bestellungen auf drei bis vier Fertiger verhindert Volumenrabatte und erschwert Prozessoptimierung. Ein konsolidierter Lieferant mit 80% des Jahresvolumens realisiert Skaleneffekte und investiert in kundenspezifische Prozessanpassungen – beides senkt Stückkosten um 10-20%.

Fehlende Fertigungsabstimmung verursacht kostspielige Redesigns. Design-for-Manufacturing-Reviews vor Layoutbeginn identifizieren problematische Spezifikationen. Ein 30-minütiges Abstimmungsgespräch mit dem Fertiger verhindert mehrtägige Layout-Iterationen und vermeidet Prototyping-Schleifen, die jeweils 2-4 Wochen kosten.

Optimierungsstrategien zur Fehlervermeidung

- Layout und Routing optimieren: Signalpfade minimieren

- Fertigungs- und Bestückungsfähigkeiten verbessern

- Simulation und Testing einsetzen: Probleme früh identifizieren

- Hochwertige Materialien wählen: Balance zwischen Performance und Langlebigkeit

- Supply Chain-Kollaboration stärken: Design effektiv umsetzen

Die systematische Anwendung dieser Strategien maximiert HDI-Kostenvorteile. Simulation kritischer Signalpfade vor Prototypenbau reduziert Iterationsschleifen. Early Supplier Involvement bindet Fertigungs-Know-how ins Design ein. Materialauswahl nach TCO statt Stückpreis optimiert Lebenszykluskosten. Diese Massnahmen erfordern marginalen Mehraufwand im Engineering, generieren aber substanzielle Einsparungen in Fertigung und Betrieb.

Die wichtigsten Erkenntnisse

- HDI-Wirtschaftlichkeit basiert auf TCO-Betrachtung über den gesamten Produktlebenszyklus, nicht auf isolierten PCB-Stückpreisen

- Mikrovia-Architektur reduziert Lagenzahl um 40-60% und setzt Kaskadeneffekte bei Gehäuse, Logistik und Systemkosten frei

- Break-even-Punkte variieren stark nach Branche: 5.000-10.000 Einheiten bei Consumer Electronics, 1.000-2.000 bei Medizintechnik

- Designfehler wie Überspezifikation, ungenutzte Mikrovia-Potenziale oder fehlende Fertigungsabstimmung eliminieren theoretische Einsparungen

- Erfolgreiche HDI-Implementierung erfordert Design-for-Manufacturing, realistische Spezifikationen und strategische Lieferantenpartnerschaft

Fazit: HDI als strategische Investition in Systemeffizienz

Die Analyse offenbart HDI-Technologie als mehrdimensionalen Optimierungshebel, dessen Wert weit über Platzeinsparung hinausreicht. Die Mikrovia-Architektur initiiert eine Wertschöpfungskaskade: Reduzierte Lagenzahl senkt Material- und Fertigungskosten. Kompaktere Baugruppen minimieren Gehäuseaufwand, Transportvolumen und Lagerkosten. Verbesserte Zuverlässigkeit durch günstige Aspektverhältnisse reduziert Garantieaufwendungen.

Diese Effekte summieren sich zu Systemkostenreduktionen von 15-40% gegenüber konventionellen Multilayer-Designs – allerdings nur unter spezifischen Voraussetzungen. Produktionsvolumina über den branchenspezifischen Break-even-Punkten, Anwendungen mit kritischen Grössenbeschränkungen und Designteams mit HDI-Expertise sind die Erfolgsvoraussetzungen.

Die grösste Gefahr liegt in der unkritischen Technologieadaption. HDI ist kein Universalrezept für niedrigere Kosten. Überspezifikation, Design ohne Fertigungsabstimmung und falsche Materialwahl transformieren Einsparpotenziale in Kostenfallen. Wirtschaftlicher Erfolg erfordert kontextspezifische Bewertung: Welche Funktionsdichte wird tatsächlich benötigt? Welche Stückzahlen rechtfertigen NRE-Investitionen? Welche Designregeln optimieren Ausbeute?

Unternehmen, die diese Fragen methodisch beantworten und HDI-Kompetenz strategisch aufbauen, positionieren sich für eine Elektronikzukunft, in der Miniaturisierung, Energieeffizienz und Kostenoptimierung simultane Anforderungen darstellen. Die TCO-Perspektive statt isolierter Stückkostenbetrachtung wird dabei zum entscheidenden Wettbewerbsvorteil.

Häufig gestellte Fragen zu HDI-Leiterplatten

Welche Branchen profitieren am meisten von HDI-Technologie?

Automotive, Aerospace, Medizintechnik und Consumer Electronics mit hohen Miniaturisierungsanforderungen profitieren am stärksten. Diese Branchen kombinieren kritische Grössenbeschränkungen mit hohen Zuverlässigkeitsanforderungen und ausreichenden Produktionsvolumina zur Amortisation der höheren Entwicklungskosten.

Wie berechnet sich der ROI bei HDI-Investitionen?

Der Return on Investment ergibt sich aus reduzierten Systemkosten (Material, Fertigung, Logistik, Garantie), verbesserten Produkteigenschaften (Grösse, Gewicht, Zuverlässigkeit) und erweiterten Funktionalitätsmöglichkeiten über den Produktlebenszyklus. Die Berechnung muss alle Kostenkomponenten vom Engineering bis zum After-Sales-Service einbeziehen.

Was ist der Unterschied zwischen Standard-PCB und HDI?

Standard-PCBs nutzen durchgehende mechanisch gebohrte Vias mit 0,3-0,4 mm Durchmesser, die alle Lagen durchdringen. HDI verwendet laserstrukturierte Mikrovias mit 0,1-0,15 mm Durchmesser, die nur einzelne Lagenpaare verbinden. Dies ermöglicht höhere Leitungsdichten, Routing zwischen BGA-Pads und Lagenreduktion um 40-60%.

Wann lohnt sich der Umstieg auf HDI-Technologie?

Der Umstieg lohnt sich bei Produktionsvolumina über 5.000-10.000 Einheiten für Consumer Electronics oder 1.000-2.000 für Medizintechnik, wenn Miniaturisierung kaufentscheidend ist, bei Fine-Pitch-BGAs unter 0,5 mm Pitch oder wenn konventionelle Technologie funktionale Anforderungen nicht erfüllt. Eine detaillierte TCO-Analyse über den Produktlebenszyklus gibt Aufschluss über die individuelle Rentabilität.